| 製程轉進3D NAND是不可避免的,但仍有許多技術需要自2D NAND微縮。一個由應用材料(Applied Materials)在IDEM上贊助的論壇討論了目前產業的情況與未來發展。 |

在iPod音樂播放器發表時,Apple衝高了NAND快閃記憶體(一種非揮發性的儲存元件)的使用量,驅使成本降低並且為目前數十億美元市場的記憶體技術鋪出一條繼續成長的道路,為不需高密度儲存需求的智慧型手機、平板電腦及其它 消費電子元件提供了具成本效益的儲存方式。

目前NAND技術的演進,2D(或平面)NAND,已達到了它的極限。在2013年8月,南韓消費電子商Samsung宣布推出3D NAND儲存技術,以24層的124GB晶片型式問世。2014年,記憶體晶片製造商Miron以及SK Hynix將仿效,宣佈了未來幾年在各產業會議上更被期待與熱烈探討的技術已經來到。其他公司,包括Sandisk,也都在發展3D NAND快閃記憶體技術。

就像高樓裡的樓層,在3D NAND元件中記憶體單元彼此往上層疊,對比於平面攤開的2D技術就如同水平格狀排列的平房。過去幾十年2D NAND技術的演進,X與Y方向上尺寸不斷微縮以推進晶片世代。但製程進入低於20奈米在朝向10奈米的路上前進時,繼續微縮是已知的挑戰,因為物理限制 會開始影響到基本記憶體單元設計的效能。僅管2D NAND還沒走到技術撞牆的盡頭,但那只是早晚的事。

過渡到大量生產

但儘管3D NAND的潛力和產業中領導廠商的技術發表,轉換3D NAND技術到量產的模式仍舊非常的具有挑戰。正如Jim Handy的客觀分析指出:「3D NAND的整個問題是其驚人的複雜度,這是為什麼還沒有任何一家公司開始有3D NAND晶片的出貨的原因。」Samsung的產品預計在今年量產。隨著3D NAND技術,垂直向的尺寸也將可調整,自16-bit字串高度到超過128-bit的字串高度。

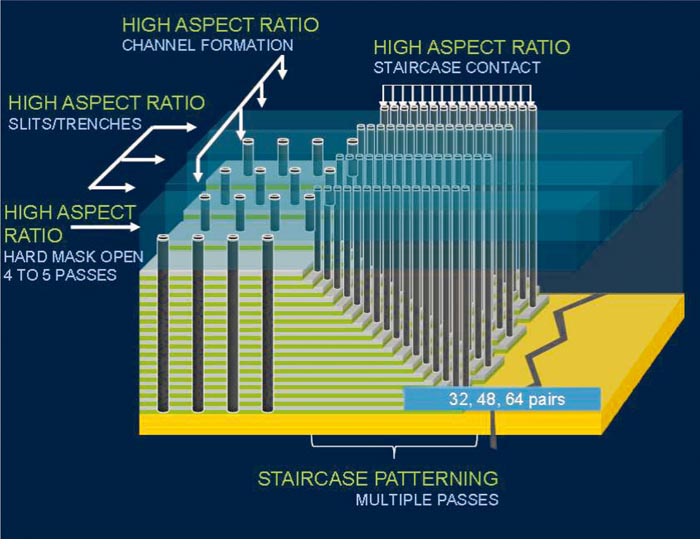

因為3D NAND不需要更先進的微影技術,終究可以達到比延展平面NAND還要低的製造成本,但是因為高的寬深比蝕刻製程將會需要新的沉積與蝕刻技術。這種「階梯」蝕刻需要非常精準的接觸著陸控制(圖一)。在3D NAND的製造上,整片晶圓均勻膜厚的沉積層對這種「階梯」的拉回蝕刻造成問題,對目前微影製程負擔的增加比原本預期的還大。

圖一:階梯蝕刻需要非常精準的接觸著陸控制

據Handy所述,「在3D的一切都是重大的挑戰。因為垂直的尺寸調整,挑戰包含了蝕刻高寬深比的孔洞,而且要蝕刻兩倍以上,有著兩倍寬深比的沉積層,這些孔洞必須有絕對平行深壁面,否則尺寸與元件操作的效能將會打折扣。如果沉積層 被蝕刻變薄,那麼這些層的原子層沉積(ALD),必須能夠對整片晶圓做到相同厚度的沉積,這對沉積孔洞壁面的薄膜層也一樣是必要的。」

的確,雖然成本、功率與效能的最佳組合將在3D NAND的架構中被找到,但是在成本方面仍然特別有問題。記憶體製造商,包括新帝(Sandisk)、海力士(SK Hynix)及美光(Micron),在一個由半導體產業設備製造商應用材料(Applied Materials)於2013年12月所安排並贊助的論壇上,根據其各自記憶體技術發展藍圖方面討論了這些問題,而設備供應商也提供了一些3D NAND製造上的考量與挑戰的深入討論。該會議是由應用材料的資深處長及矽系統群的技術幕僚之首席成員Gill Lee所主持。

新帝(Sandisk)盡其可能的延伸使用其2D技術

新帝公司的技術研發副總Ritu Shrivastava陳述其挑戰。「當你講到技術,必須要與公司目標連結。對我們而言,我們有到2016年總值380億美元的市場預估,我們所做的任何 技術選擇必須能夠支援這樣的市場。」他所提的產品例子包括智慧型手機和平板電腦。「我們的目標是選擇最具成本效益並且可以提供所需性能的技術。」

新帝有一個與東芝(Toshiba)共同投資的NAND晶圓廠,他們已有128GB 2D NAND快閃記憶體晶片使用19奈米微影製程生產一段時間了,並在前一陣子宣佈要蓋一座生產16-17奈米快閃記憶體的半導體晶圓廠的計畫。

「我們的目標之一是盡可能的延長2D NAND技術的壽命,因為它反映了過去幾年我們在晶圓廠與技術上所做的巨大投資,」Shrivastava如是說。「當然,3D NAND是極為重要的,當它變得具成本效益後將會很快進入生產。」新帝計畫在2016年開始生產它的3D NAND晶片。

他補充道,「我們正行駛於每個技術世代中,我們認為最低成本的路徑上,正由19奈米到處於微影製程極限的1Y,然後我們將再微縮進到1Z,此為我們的下一世代2D NAND技術。在考慮了累計的投資後,我們相信這樣的微縮路徑會帶給我們在各個技術世代中最低的成本結構。」

但這並非僅是達到最小的顆粒尺寸,它是成本牽扯於尺寸微縮中。根據Shrivastava,資本設備的投資是這個市場上決定成功的因子。「儘管我們說3D NAND是個事實,有幾件事我們必須記得。它利用現存的基礎設施,這是好的,但是仍然有許多的挑戰。3D NAND元件使用TFT相對於在2D NAND晶片上一般使用的浮動閘極元件。將會需要新的控制器設計以及電路板件。」

因此根據Shrivastava的說法,3D NAND看起來非常有前景,但對於像新帝這樣在市場上生產一些最具成本競爭性的快閃記憶體元件的公司而言卻有個很大的「但是」。「2D NAND仍然持續比3D NAND有成本效益,且3D NAND還沒被驗證能夠量產。每個新技術都需要一些時間。達到大量生產會花一些時間。我們的目標是盡可能的延長2D NAND,持續進行3D NAND的發展,然後當它變的具成本效益時再導入。」

Shrivastava看到2D與3D NAND技術在未來的十年中將共同存在。3D NAND以外該公司也在開發一種3D電阻式RAM(RRAM)當作超越3D NAND後的未來技術。

由3D DRAM到3D NAND

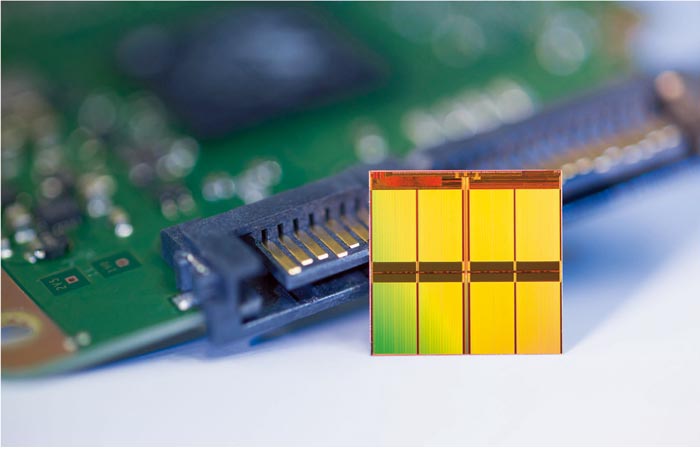

接下來美光的製程整合資深處長Chuck Dennison提供了他們公司目前技術的概況,以公司的NAND記憶體技術發展藍圖顯示。根據Dennison所說,「我們目前的世代是16奈米 NAND目前正在量產,我們正展現它逐漸成為一個非常有競爭力並且具成本效益的技術。」美光的新16奈米NAND製程提供任何多階儲存單元(MLC)元件 在每平方公厘面積上有最大量的位元(bits)數及最低的成本。八個這種晶粒便可儲存128GB的資料。這個16奈米的儲存技術將在2014年被應用在下 一代的固態硬碟(SSDs)上。SSDs由內部連結的快閃記憶體晶片所組成,相對於傳統硬碟(HDDs)使用磁性塗層的碟盤。美光的16奈米晶片如圖二所 示。

圖二:美光16奈米NAND晶粒

「我們的下個世代是256GB級別的NAND記憶體。技術上它可以在完整採用3D NAND之前由目前的技術推展出來,」他如是說。在今日, NAND是最低單位位元成本的記憶體技術,而持續的單位位元成本下降真正驅使著整個NAND產業,根據Dennison所述。這是為什麼NAND在總產值 上已取代 DRAM,且持續擴展到其他許多應用上,它也在可攜式消費電子商品領域中(如平板電腦,會將很多如拍照、攝影、儲存整個音樂庫等等功能整合包裝於一個元件 裡)帶領與提供持續的創新。

概述美光的技術微縮進程時Dennison解釋:「我們使用high-K金屬閘極來達到20奈米,我們也使用相同的技術來延伸到16奈米。自此,公司將會進入垂直通道3D NAND的技術來生產256GB等級產品。」

Dennison解釋道,「由於high-K金屬閘極技術,就每片晶圓的資本支出(CapEx)而言都有成本效益, 」轉換20奈米時有些微變動,進入16奈米時也只有極小的增加。「但是進入3D NAND每片晶圓成本將會非常昂貴。如果你增加了晶圓成本X的量,你必須增加更多的位元數在每平方公分的晶圓面積內,因此我們選擇這樣的密度在256GB 等級產品上。而且當你開始積極注意3D NAND時會發現3D NAND與DRAM有許多相似處,」他參考堆疊電容的DRAM又解釋。「它會有很多的平坦化,你必須蝕刻很大寬深比的接觸線,因此在如何定義控制以及臨界 尺寸的均勻度上需要很好的控制。然後會增加許多模組需要 ALD沉積。因此我們認為會有很多機會可以利用我們的DRAM專業知識。」

他再次概述了自16奈米往下會出現的轉折點。「我們正在過渡進入256GB密度。我們認為僅管有高的資本支出,當我們這樣做時它必將符合財務意義,並且是具有成本效益的解決方案。然後我們將由此處繼續下去。在主流(或大量)市場我們將看到立體NAND持續微縮,其中部分如我們的廠商會快於市場的微縮需求。」

Dennison也提到快閃記憶體等級的長期發展,基於3D交叉點技術觀點。它是記憶體以交叉點陣列堆疊於CMOS邏輯上以達到記憶體技術有近DRAM的 速度但密度與成本效益卻近似NAND。未來,3D交叉點技術的3D堆疊記憶體陣列將使得元件適合用在非常高密度計算甚至是生物系統上。

「但是,總結而言,NAND將不會被取代,而且將持續展現最低成本,將佔有平板電腦、電話等等的最大市場。它不是最好的記憶體技術-它有差勁的耐久性,以 及可怕的傳輸延遲-但它有很高的密度與很低的成本,因此是最具成本效益的解決方案。我們認為3D交叉點技術絕對有機會取代DRAM或選擇性的取代一些 NAND在非常高性能的應用市場上,但我們會繼續支持NAND並朝向3D NAND發展。」

海力士副總與快閃裝置技術群的負責人Soek-Kiu Lee讓參與者了解他們公司的NAND技術。海力士每年提高約50%的單位面積上的位元密度。該公司採用浮動閘極技術的16奈米64GB MLC NAND快閃記憶體已於2013年中開始生產,代表著海力士現已進入16奈米晶片全規模的量產。海力士將在今年開始出貨3D NAND晶片的樣本,其量產時程預計在2014年尾。

如同Shrivastava, Lee預期2D NAND與3D NAND將共同存在,並在可靠度、效能以及密度上相互競爭一段時間,然後轉換到3D NAND架構所面對的大挑戰包括多層疊圖樣化的穩定度以提升良率,以及在本身3D架構中更好的量測與缺陷檢查能力。

提到高度

最後,應用材料提供了一些製造生產更複雜結構的洞見以進入3D NAND元件架構所需。非常簡單的說,做3D NAND快閃裝置需要建造極度高的多層結構。裝置中的每一層需要一層絕緣層,例如,一個32層的裝置實際上是ㄧ個64層的裝置。這樣的結果是,該被蝕刻出 來的結構其寬深比變得非常高,而這造成的挑戰無異於改變了蝕刻與沉積製程及設備的遊戲規則,根據應用材料先進技術群蝕刻事業處副總Bradley Howard敘述。

他說道,「就歷史經驗,如果你看過去尺寸微縮的演進,進入下一世代更小尺寸總是限制在微影製程,現在我們已經到了沉積與蝕刻製程驅使尺寸微縮的時候了,因 為現在的尺寸微縮是在垂直方向上以簡化設計規則。」Howard接著說,「事實是微影製程依然重要,在列出控制、好的均勻度與其他因素後。以前你需要微影 製程的所有條件依然成立,只是它已不必然為尺寸微縮的限制因子了。」

大的寬深比帶出許多挑戰。標準黃光微影將無法支撐蝕刻出深溝容貌所需的長久蝕刻,因此需要硬屏蔽層。「沉積製程正由單層沉積典型的薄膜轉換到多層堆疊,此處由沉積堆疊層膜與非常厚的膜交錯進行於裝置層及硬屏蔽層,」Howard說。

Howard提到了閘極軸,交錯的材料堆疊建立了交錯層。「你必須有非常精準的控制與非常低的缺陷率。就歷史經驗,如果一個缺陷出現在一層膜上,它會影響 到那個位元,或那個區域。現在如果有一個缺陷被沉積在最底部的第一層,它變成一個會傳播的缺陷,會往上出現在整個堆疊且影響上面整個區域,這表示沉積的缺 陷密度變的更加重要。」

Howard接著講到硬屏蔽層。「我們將需要更厚的硬屏蔽層因為你試圖蝕刻的寬深比以及你要蝕刻的深度都變的非常極端。出現1微米或1.5微米的硬屏蔽層 並不會不尋常。實際上,你形成的硬屏蔽層本身有大的寬深比容貌,然後它形成往下需要的大寬深比容貌。此外,兩個容貌間以及這些非常複雜的三維縫隙填補的絕 緣工作有各種的挑戰存在。

「大的寬深比在蝕刻部分是 非常關鍵的。在陣列中有很多容貌與接觸面,階梯帶出許多接觸面,60:1的寬深比在這裡變成是個通常的目標值。

「在陣列的邊緣每一層的存取仍然要做,所以階梯結構是為了接觸面下來用的不同著陸版。但是ㄧ些接觸面-朝上層-顯得很淺,而那些下面的則非常的深。

「你也許覺得可以透過一個黃光步驟和一個蝕刻步驟,再一個黃光步驟和一個蝕刻步驟,如此進行32或64次或無論幾次,但情況是你從一個容貌開始,你蝕刻掉 那個容貌然後拿掉光阻,然後再蝕刻,再拿掉光阻,如此你開始做出你的『階梯』,盡可能的重複這樣的動作,光阻的量會決定你的進行次數。所以,你可以想像你 試著很快的拿掉光阻。問題是光阻現在會決定 單元的CD,因此你需要有好的控制方法。」Howard總結關於沉積和蝕刻與厚膜的連續製程的挑戰-不論是交錯層疊膜或是厚膜用來分開不同的陣列-以及最 後,缺陷密度-特別在沉積製程-會變得比過去更加關鍵,因為沉積製程的加乘作用。

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

|