IC產業一直是十分具有創新理念的產業,許多新穎的技 術與材料都獲得採用,例如應力源(stressor)以及high-k金屬閘的設計 (high-k metal gate, HKMG)。因此相較起來維持現有的平坦式電晶體架構是非常保守的作法。也因此在尺寸縮小的情況下平坦式電晶體的摻雜濃度必須提高。在縮小尺寸的要求下,電晶體特性受到統計變異的影響也越發顯著,例如通道中的隨機摻雜變異 (Random Dopant Fluctuation, RDF) 造成尺寸在100nm以下電路的匹配性降低。這個問題在28/32nm以下的元件中更為嚴重,使得VDD無法下降,也因此無法降低動態與待命時的功率耗損。

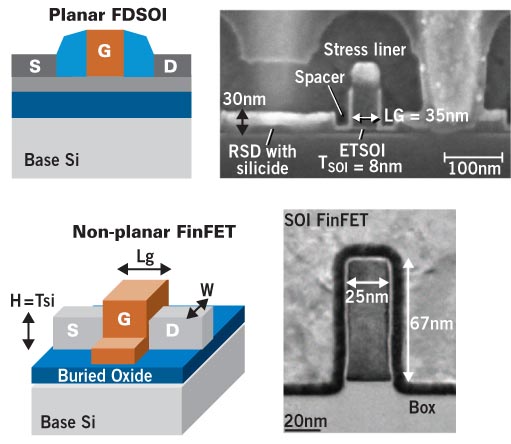

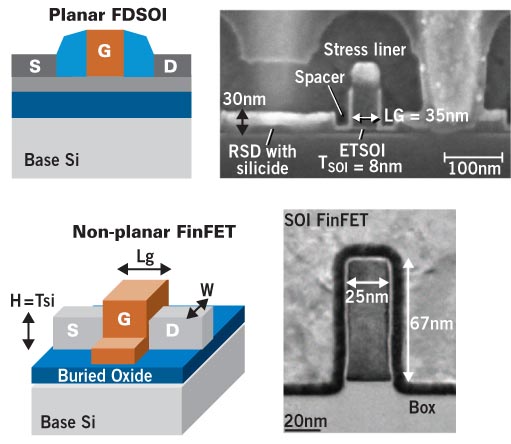

在IC產業大家都有的共識是全空乏型(fully depleted, FD)電晶體,或被稱為超薄體 (ultra thin body, UTB) 元件,是解決VT因為隨機摻雜變異 (RDF) 而出現擾動的問題。FD元件可以是垂直式結構 (FinFETs, 3D MOSFET) [1] 或是平坦式結構 (FD-SOI) [2, 3]。它們的共同特徵是通道都沒有經過摻雜處理 (圖一)。

圖一:全空乏元件之實例:a)平坦式FD-SOI或者超薄體UTB (感謝IBM提供TEM照片);

b) 3D FinFET元件 (感謝IMEC提供TEM照片)

FD- SOI是一項劃時代的技術因為它有平坦式結構的優點並且以現有的設計以及EDA工具延展了傳統體元件設計(bulk design)流程的適用性。這項技術對SOC的設計與製程而言是一種非破裂 (non-disruptive) 的MOSFET結構。為了改善電性特性 [3],FD-SOI需要在極薄的下埋氧化層(buried oxide, BOX<25nm)上形成一極薄的矽層 (<20nm)。FD技術具有許多好處,包括功耗減少、尺寸微縮、特性改善以VDD 降低等優點 [3]。整個IC SOC領域都同意當尺寸微縮到20nm以下時必須使用全空乏(FD) MOSFETs。

為了精進CPU晶片的效能,Intel率先在2011年推出3D FinFET元件 [1]。另一方面晶圓代工產業則是將傳統的CMOS技術從28nm微縮到20nm。元件密度的提升伴隨的是單位面積的成本升高,可是在性能上的優化效果卻 相當有限。的確當尺寸小於28nm以下時,採用雙顯影(double-patterning)技術的20nm CMOS元件與採用3D FinFET的14/16nm CMOS元件就會變得非常複雜。技術節點上的提升所帶來的特性改良小於30%,低於過去我們觀察到每次技術節點提升時的優點。

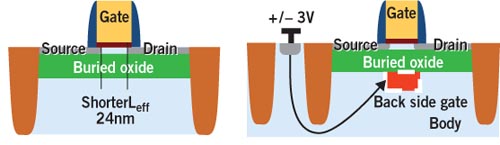

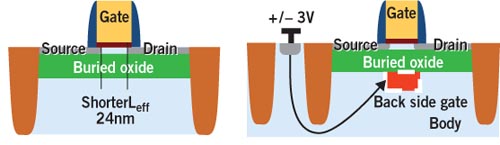

圖二:28nm FD-SOI電晶體的示意圖:a)在下埋氧化層上具有薄層通道的FD-SOI MOSFET的橫截面;

b) 摻雜井的電位透過下埋氧化層下方的閘極變成電晶體的底部偏壓。

在上述情況下,28nm FD-SOI [4, 5] 就成為一項十分吸引人的替代方案,因為它是HKMG架構中功率耗損最低的選項。事實上28nm FD-SOI不需要微縮尺寸就可以發揮特性提升的優點。對低功率IC而言這是一項非常有吸引力的選項,因為對該應用而言面積不是關鍵,但是在相同或是更低 的功耗條件下,運作效益的提升才是重點。因此從功耗、效益以及成本上來考量,許多IC產品轉而使用FD-SOI生產而不需要汲汲於尖端技術的使用。只有受 元件密度影響甚大的IC產品才需要在技術節點上尋求突破。晶圓代工廠若能提供28nm FD-SOI技術 [6] 無疑地將吸引許多無晶圓設計公司的興趣,因為它們現有28nm的產品特性能夠以這套第二代28nm元件技術在不犧牲低功率操作的優點下將效益提升。此外 28nm低功率HKMG FD-SOI技術將會吸引眾多的40nm IC產品向28nm靠攏。

FD-SOI技術

對傳統的Bulk MOSFET而言,通道VT的值是藉由通道佈植與環形(halo)佈植加以調整,而這正是RDF的來源。相反地,FD-SOI的通道是無摻雜的,因此可以 顯著地降低或徹底消除RDF的問題。FD電晶體的VT是藉由閘極的功函數(work function) 以及基板偏壓 (back-bias) 加以調整。FD-SOI電晶體由於具有較佳的靜電特性,因此元件的寄生效應較小,電晶體的驅動能力也獲得改善。也因為有較佳的靜電特性,使得它的短通道效 應與傳統28nm元件相比較為輕微。如此一來CMOS元件的通道長度可以稍微減小(Lg=24nm),源極 (source) 與汲極 (drain) 的接觸窗尺寸的製程限制得以放寬。

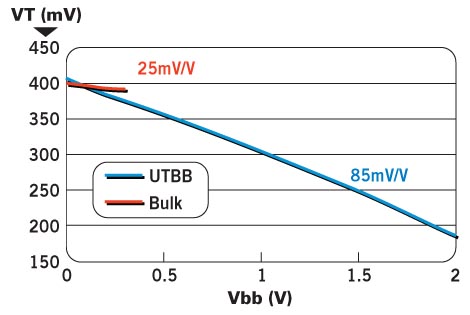

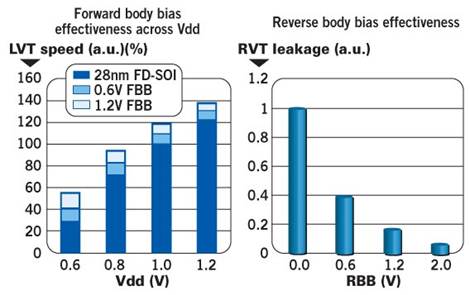

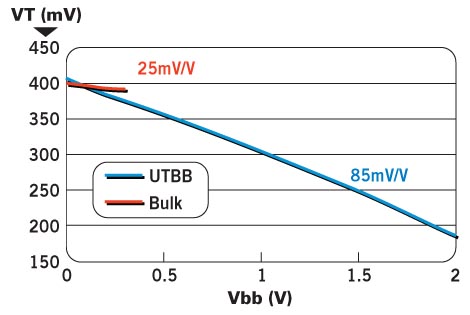

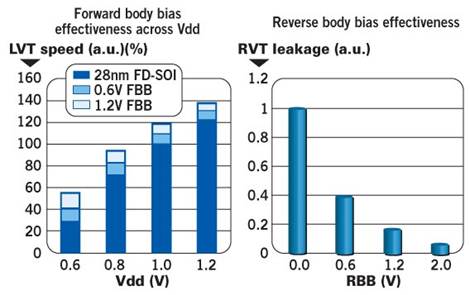

具有超薄體以及下埋氧化層(ultra-thin body and buried oxide, UTBB) 的FD-SOI [2, 3] 可藉由在基底施加偏壓的方式提供調整FD電晶體特性的優點 (圖三a)。理論上此FD-SOI電晶體是由兩個閘極控制,一個是原有的閘極,另一個是在背面的獨立閘極。過去在電路上執行順向(FBB)與反向基底偏壓 (RBB)的技巧已經被許多設計者廣泛地使用,但是偏壓範圍有限。另一方面,藉由順偏源極/汲極與摻雜井構成的二極體,加上因為通道摻雜濃度上升因此VT 受基底偏壓的影響降低,UTBB可以延展基底偏壓的範圍到數個VDD 的程度(-3V<VBB<+3V)。如圖三b所示,這對電源管理以及效益提升而言是一項非常有用的設計工具。尤有甚者,FD-SOI技術還可 以動態地調整臨限電壓VT。

採用基底偏壓技術所衍生的額外面積 (area overhead) 非常有限 (2-3%) 因此可以限縮在IPs中(也就是CPU/GPU核心),也因此減少施行上的困難以及額外的面積需求。

圖三a:VT與基底偏壓之間的關聯性 [4]

圖三b:順向與逆向基底偏壓與提高速度與節省功率之間的關聯性

28nm的FD-SOI 製程是改變自傳統的28nm HKMG LP技術。它使用相同的後段製程以及相同的閘極模組,輕易地就將傳統的28nm製程予以增值式地轉換,甚至還可以使用相同的設備進行製造。與傳統的 28nm技術相比,有些製程步驟特別是通道離子植入、環狀植入、以及光罩數量,因為FD-SOI的通道是不需要摻雜所此可以除去。與傳統的CMOS製程相 比,製程轉移所造成的改變還不到20% [4,6]。

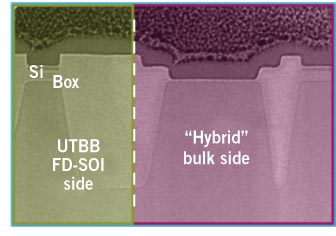

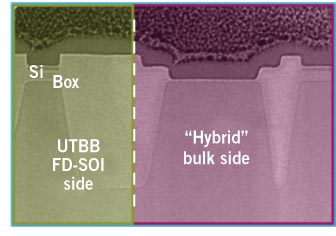

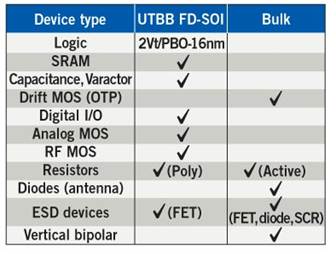

具有超薄體(thin body)和下埋氧化層的結構讓設計者可以蝕刻並且可以將SOI元件和傳統元件整合在同一個的SoC中 (圖五)。為了單純起見,ESD和I/O結構仍然以傳統元件方式設計 (圖四b),也就是以傳統結構製作出二極管和雙極電晶體的混成單元 [2,3,4]。

圖四a:在單晶片中整合SOI與傳統元件

圖四b:可應用28nm FD-SOI技術的元件分類

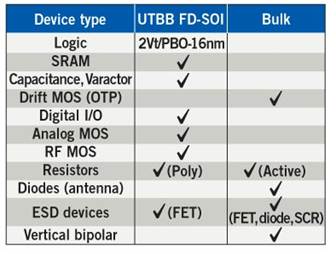

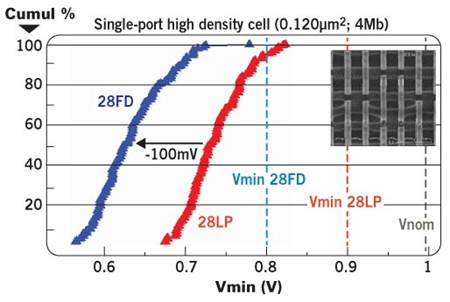

圖五:傳統28LP與28nm FD-SOI之6T SRAM之特性比較

FD-SOI基板

FD-SOI的技術基礎是在SOI基板上還有超薄頂矽層(<12nm) 和超薄下埋氧化層(25nm)。整片晶圓上任何一點的厚度均勻度都要符合6σ = ±0.5nm [8]。

超薄矽:超薄矽的初始厚度與隨後的FD CMOS製程必須互相匹配。由於清洗步驟以及犧牲氧化層會消耗一些表面的矽材料,因此在設計SOI的初始厚度時必須考慮到上述的厚度損耗。矽通道的厚度目 標通常在5nm到7nm之間 [3, 7]。SOI的厚度 (TSi) 對MOSFET的元件特性有直接的關聯性 [5]。若要利用FD-SOI改良靜電特性的話,可參考經驗法則:LG =1/3 TSi (5) 估算通道長度。

厚度的均勻性是控制平面式FD-SOI VT變異與短通道效應 (short channel effect, SCE) 的重要參數。通常對均勻度的要求包括晶圓上的均勻性和晶圓與晶圓之間的均勻性。兩者結合在一起就是所謂的總厚度變化 (layer total thickness variation, LTTV),並且定義整個製作過程中製程容忍的厚度均勻性。所有SOI晶圓以及所有點測位置上的LTTV必須是在奈米或奈米以下等級的範圍內以滿足FD的 規格標準。

從電路與元件方面來考慮,晶圓內 (within wafer, WiW)、整片晶圓TSi的不均勻性和晶圓與晶圓之間 (wafer-to-wafer, WTW) TSi 重現性的最大可容忍的TSi 波動是 ±5A。

超薄BOX:薄BOX (下埋氧化層) 可抑制電晶體源極、汲極和通道透過厚BOX彼此之間出現橫向靜電耦合。此外,降低BOX厚度可改良FD-SOI的微縮能力,厚度接近定值的通道長度可以降 到LG=10nm,恰好對應閘極目標長度10nm的技術節點。超薄BOX (ultra-thin BOX, UTBOX) 結構允許使用基板偏壓以及正向偏壓的方式在更寬廣的VBB範圍中調整電晶體的電性,其中包含導通電流 (Ion),關閉時漏電流 (Ioff) 以及臨限電壓VT [9]。

BOX的厚度TBOX和矽的厚度TSi在SOI製程中是彼此獨立的參數因此可以加以調整而不會劣化上方矽層的特性。超薄BOX的氧化物品質與等效閘極氧化層的品質非常接近。

FD-SOI設計

我們使用標準的商用EDA流程設計傳統型和FD-SOI元件。從傳統元件轉變為FD-SOI元件的EDA流程非常簡單而且內連線與繞線 設計都是相同的。如果TSi夠薄 (<10nm),因為沒有記憶效應也沒有浮體效應,FD-SOI的元件特性將非常類似傳統電晶體元件。邏輯和記憶體元件的設計和架構也與傳統元件類 似。

FD-SOI和傳統元件之間的差異在於製程與設備的不同,此外包括SPICE模型、ESD與類比元件的整合,以及利用基板偏壓的作法。

標準和客製化的 FD-SOI 元件可以從現有的傳統元件予以複製或是導入。由於是不同的SPICE模型所以需要重新測量元件特性,資料庫中的數據包括輸入電容、時序、漏電和動態功率數 據都會改變。時序分析需要重新運行以確保沒有因為直接導入而出現衝突的意外。將傳統元件轉變成 FD-SOI 元件就像是轉移到一個新的傳統元件設計一樣簡單 [10,11,13,14]。

元件模型是實際以FD-SOI結構進行驗證,同時也有EDA工具支援。簡明的元件模型 [11,12] 已經做好生產準備。

實際電路之結果

SRAM的強韌度 (robustness):FD-SOI因為它的通道未經摻雜,因此RDF大幅減少並且具有最低的AVT [3,9]。如此一來與傳統SRAM元件相比,FD-SOI的尺寸可以最小化並且以較低的VDD操作。FD-SOI元件具有更好的讀取穩定性和讀寫能力。 傳統元件為了補償VT變異而提高VDD或是增加通道長度和寬度的作法就再也不需要了。與傳統元件相比,FD-SOI在同一單元面積條件下可以獲得 100mV到200mV的Vmin 優勢 [4]。可以在VDD<0.8V的電壓下操作對移動手持式應用是非常具有吸引力的。

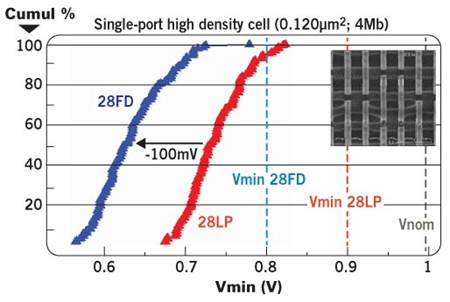

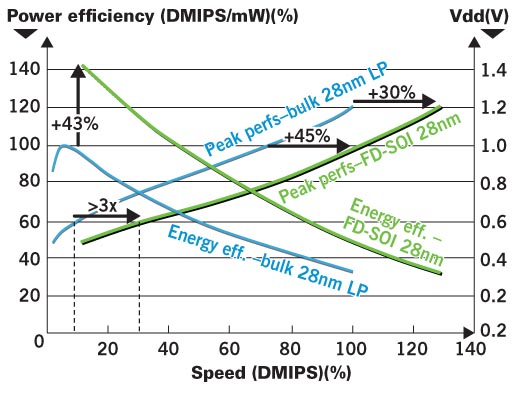

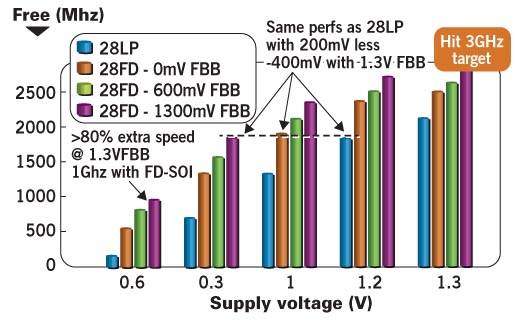

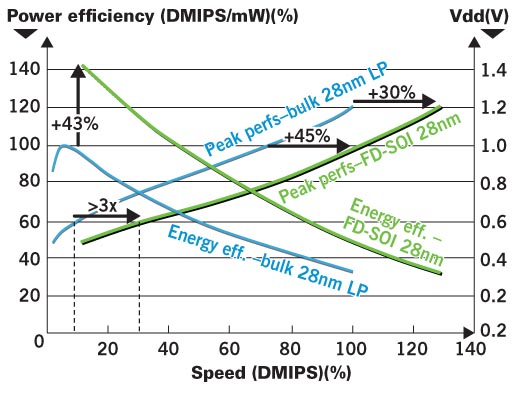

電路的性能:FD-SOI特別適用於高速且低電壓操作,如此可以顯著降低功耗 (〜VDD2)。圖六說明兩個潛在的優化路徑:(1)相同功率但是效能顯著提高,(2)相同性能但是功率顯著下降。

圖六:比較28nm FD-SOI與28LP傳統元件之最佳核心效率

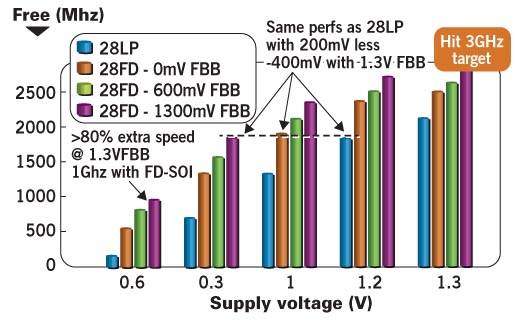

圖七:FD-SOI能夠以較低的VDD達到高速操作的優勢。此處以ARM A9核心為例,並且是實測值。

圖七顯示在不同的VDD電壓下採用FD-SOI的優點。在0.6V的偏壓下FD-SOI已經能夠提供550MHz的高頻操作,這是超過三倍等效28LP技 術的性能,並且不需要任何正向體偏壓 (forward body bias, FBB)的幫助。假如使用正向體偏壓就可能可以在0.6V偏壓下達到1GHz的操作頻率。

FD-SOI可以在比傳統元件更低的操作電壓下提供相同的性能。如圖七所示,我們的28nm FD-SOI可以用比28LP低200mV的操作電壓達到與28LP相同的性能。假如用上正向體偏壓技術則可以更進一步降低200mV。降低400mV的 偏壓需求是十分有吸引力的特性,可以立即轉化為龐大的功率節省誘因。

在過載情況下我們用FBB技術以提高性能並達到3GHz的操作頻率 [13],這是超過目前最新A9架構的操作頻率。

結論

FD-SOI技術的發展目標是在低壓VDD操作條件下達到高速的操作效能,該類元件運行時的溫升不高,能夠縮小有限的電池能量和智慧手 持系統在電力需求之間的差距。此技術的工業生態系統包括基板供應,技術平台的建立和基礎設施到位。FD-SOI技術平台非常適用於移動裝置的IC單元因為 這些單元要求極低的功率耗損以最大限度延長電池壽命。此外,由於它的單純性以及保持平面式的元件結構,FD-SOI是從傳統元件走向完全耗盡設計的一項劃 時代的進步。 SST-AP/Taiwan

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

更多歷期精采文章,請參閱智權報總覽 >>

|