僅管過去三年來自許多測試載具有一連串令人鼓舞的成果,但基於TSV的3D堆疊技術尚未成熟到足以量產的程度。對多數研發者選擇的TSV和製造技術而言這是真的,也就是以銅填充TSVs與薄化晶圓同時但分別進行會需要對載體晶圓黏合/剝離。以銅填充TSVs的問題已出現許多年並影響電路設計。現在,另一個關於薄化晶圓的TSVs剝離問題,如壓裂以及後續的處理,已經有新黏著材料研發來解決,此種材料可被雷射解聚合,且移除薄晶圓而沒有應力殘留。上述問題已有3D堆疊記憶體的創始製造商進行研究並試圖避免。令人費解的是,為什麼這種TSVs的替代材料與製造流程不是由像美國代工廠有著技術背景來進行,而是由一個沒有半導體商業生產的歐洲小國的國家實驗室來從事! |

|

由於克服依摩爾定律在進行電晶體微縮的技術挑戰,有越來越困難且昂貴的趨勢,越來越少的半導體製造商能夠升級到下個進階的製程世代(如20奈米)。因此許多在既有面積上塞入更多電晶體而不需微縮各別原件的替代方案便被積極的追求討論。這其中許多都涉及到利用3D堆疊來減少所占面積與原件之間相互連結的長度。

其中有一家具領導地位的記憶體製造商才剛公布了3D NAND產品,其電路系統是在同一片晶圓裡,將一層建構在一層之上,以在一定面積中達到較高的原件密度,而不需要發展較小的電晶體。然而當不規則的非記憶體架構(如感測器與CPUs)要被整合成3D時,此種整合可能並非輕易可行的。類似的限制也會發生在需要非常不同製造流程的原件(如類比與數位處理器和記憶體)之3D整合。

對於會需要整合有著非常不同的設計與製程晶片的一些應用,在封裝層級做整合成為一個可行的替代方案。對封裝層級整合而言,3D堆疊各別晶片是透過微縮堆疊內個別晶片間的連結長度,來減少所占面積與提升效能的最終結構配置。此封裝技術已量產應用於需要將影像感測器緊密連結到信號處理器的照相機模組上。其他的應用,例如3D堆疊DRAM晶片與CPU/記憶體堆疊,則仍在研發中。對於這些應用,選擇3D模組的技術不僅是要減少其外型尺寸,更要縮短其個別晶片間相互連結的長度。

相互連結是必要之惡

對一個晶片或系統設計者而言,電晶體之間的相互連結或晶片間的接線是一個必要之惡。它引進寄生R、L、和C到信號路徑中。晶粒層級的相互連結問題在至少二十年前就被認知到了,因為於CPUs的相互連結中出現RC延遲,造成操作超過2GHz的障礙。這個促使了晶圓層級的相互連結所需材料上的重大改變。在導體上,此轉變是由鋁到低電阻銅的使用來達到幾何尺寸上的微縮。影響寄生電容的周圍層間介電質由二氧化矽換成許多低、甚至超低K(介電係數)材料,僅管他們的機械性能較差。類似的改變甚至更早發生在晶片封裝領域,當陶瓷基材被低介電的有機基材取代時就已發生,且又能降低成本。封裝與印刷電路板(PCBs)中的相互連結也引出寄生電容,導致信號失真,以及可能限制最大頻寬的可能。發射數位訊號時相互連結的寄生電容發生的功率損失與電容和頻寬直接相關。當提高頻寬時,甚至發生在電池驅動的消費電子產品(如智慧手機)上,封裝與印刷電路板(PCBs)中的功率損失甚至更顯著(30%),雖然晶片本身的損失已透過較佳的設計(例如有低電容的ESD結構)來減少了。

改善封裝層級相互連結的效能

早在十幾年前,晶片封裝的世界經歷了一輪縮短相互連結長度與提高相互連結密度的改變,特別針對高效能的晶片如CPUs,當時傳統的周邊打線接合技術被錫鉛凸塊面積矩陣覆晶技術所取代。相互連結長度減少了一定程度,並伴隨降低寄生效應與提高和相臨晶片間資料傳輸的頻寬,例如DRAM資料緩衝區一般。然而,此電子效能的提升是來自機械複雜度增加的代價,因為矽晶片與有較大熱膨脹 係數(矽的6~10倍)的基底材結合更加緊密,使銲錫凸塊之間的相互連結受到循環應力攻擊,並會傳送部分應力到晶片本身。其所造成的晶片封裝交互作用 (CPI)會因為較大晶片與晶片上較弱的低k介電質而變得更糟。

晶片封裝技術的最新發展是應用矽導孔(TSVs)的3D堆疊,矽晶圓上蝕刻許多導孔(直徑5微米且越來越小)然後填入導體金屬,例如銅或是鎢。晶圓或切割的晶片就垂直堆疊且互相接合在一起。應用TSVs的3D堆疊提供了堆疊晶片間最短的相互連結長度,並且提升頻寬,改善資料傳輸所需功率的效率以及所佔的面積。然而,如同我們將在後面會看到的,3D TVS技術的延宕不僅是因為經常討論到的複雜物流問題,而事實上是源自於選擇了最共通變異的技術性問題:TSVs填入銅,同時晶圓薄化也在進行。

等效電路的封裝

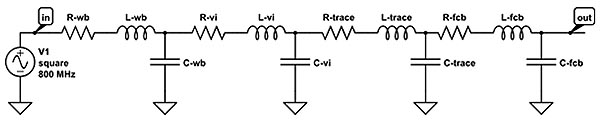

PoP(Package on Package, 層疊封裝技術)是一種使用目前非TSV技術的假3D封裝,普遍使用在智慧型手機裡。在PoP中兩個封裝(DRAM和SoC)相互層疊且周圍由銲球或銲條連結。PoP封裝總是被說是TSV應用3D層疊技術將取代的目標。在PoP中SoC到DRAM的相互連結有4個各別的元素串聯一起(DRAM封裝內的銲線、頂部和底部封裝間的垂直相互連結、SoC底部封裝的基板線路與覆晶)。典型PoP中封裝層級相互連結的等效電路如圖1所示。

圖1.在PoP封裝中DRAM與SoC晶片之間相互連結的等效電路圖。

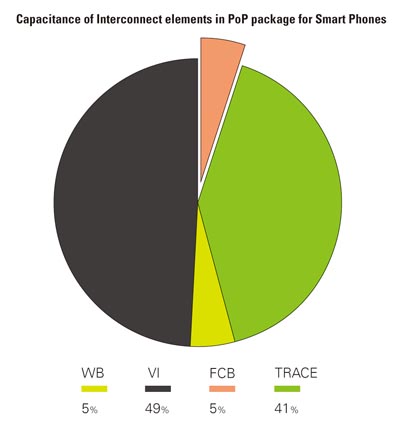

由圖2可以看到PoP封裝中相互連結的電容不僅由銲線(DRAM)所支配,也受到覆晶(SoC)封裝基材中的側向線路影響。兩個較大的貢獻在 TSV的3D堆疊技術中都被排除了。

圖2.在PoP中內部封裝互連的許多成分對電容貢獻的分解圖。總數可能超過2pF。

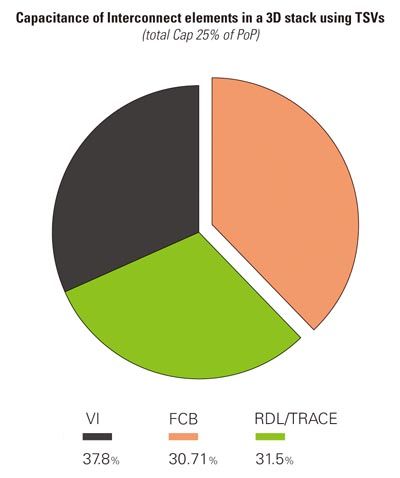

在使用TSVs的3D封裝中移除CPU與DRAM間的基材線路和銲線導致相互連結電容降低75%(圖3),並且提升了最大頻寬與工率效率。

圖3.當TSVs(標記為VI)取代傳統的PoP封裝之相互連結,晶片間(如 SoC與DRAM)相互連結的寄生電容會降低75%。

寄生效應

相互連結的寄生效應不僅造成資料傳輸時的功率損失,也影響到數位訊號的波型。對於有著給定輸入/輸出緩衝特性的晶片,較高的電容會減緩其上下緣[1,2]。電感造成更多雜訊並壓縮眼圖。因此較高的相互連結寄生效應會限制透過一個封裝或PCB的無錯資料傳出所需的最大頻寬。

基於TSV的3D堆疊

如先前已經提到的,發展TSV技術的一個主要原因是用它來改善晶片間的資料傳輸-以頻寬與功率效率衡量,並且突破傳統相互連結所造成的頻寬限制。最近西歐的一個國家研究室發表堆疊一個單一DRAM晶片到一個特別設計有 TSVs在4x128位元寬I/O格式與200MHz時脈下操作的SoC之試驗結果[3]。他們能夠示範12.8MB/sec的頻寬(兩倍於在PoP中有 LP DDR3在800MHz下操作)。試驗報告資料傳輸的功率效率(0.9pJ/bit)僅是PoP情況的四分之一也不令人意外。

僅管過去三年來自許多測試載具有一連串令人鼓舞的成果,但基於TSV的3D堆疊技術尚未成熟到足以量產的程度。對多數研發者選擇的TSV和製造技術而言這是真的,也就是以銅填充TSVs與薄化晶圓同時但分別進行會需要對載體晶圓黏合/剝離。以銅填充TSVs的問題已出現許多年並影響電路設計[4]。問題來自銅和矽之間巨大的熱膨脹差異,其造成的應力留在銅填充的TSVs區域周圍會改變電子遷移率與電路效能。最直接的解法是在TSVs周圍建立排除區域,然而這會影響晶粒上相互連結的路徑與長度。因為銅填充的TSVs周圍的應力區域是穿孔直徑的平方,較小直徑的TSVs已在研發中來縮小排除區域。

現在,另一個關於薄化晶圓的TSVs剝離問題,如壓裂以及後續的處理,已經有新黏著材料研發來解決,此種材料可被雷射解聚合,且移除薄晶圓而沒有應力殘留。

上述問題已有3D堆疊記憶體的創始製造商進行研究並試圖避免。他們將穿孔的填充材料由銅改為鎢,鎢的熱膨脹係數(CTE)差異較銅來的小,並且被選用在堆疊晶圓的後續黏合/薄化製程,因此完全避免了黏合/剝離或薄化晶圓處理的任何問題。

這是令人費解的,為什麼這種TSVs的替代材料與製造流程不是由像美國代工廠有著技術背景來進行,而是由一個沒有半導體商業生產的歐洲小國的國家實驗室來從事!

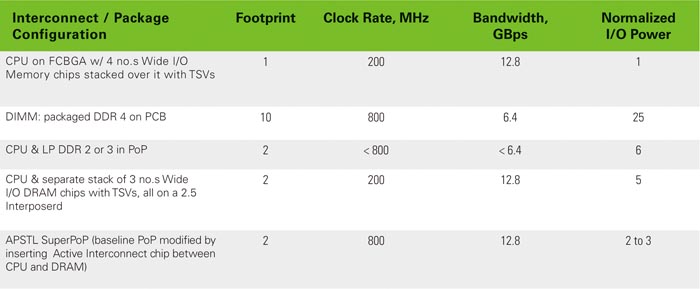

CPU到記憶體的整合替代選項

已知使3D TSV技術用在晶圓代工的時程會延遲,類似2.5D的替代方案(例如在高密度有TSVs的矽基底材上的平面複晶片模組,MCMs)已受到許多注意。然而2.5D在矽基底材的額外成本必須從效能,以及/或是所佔面積的角度來驗證合理性。2.5D模組中兩個相鄰晶片間接線造成的相互連結寄生效應遠比用封裝的晶片建系統的PCBs小很多。但他們還是比真的用TSVs做3D堆疊所可能達到的程度大上許多。因此建立一個使用TSVs的CPU與相鄰堆疊記憶體晶片的 2.5D模組可以降低矽基底材的尺寸與成本,但無法全部呈現與CPU和記憶體做全TSV 3D堆疊一樣的效能。

封裝層級整合的TSVs替代選項

整合非制定CPU到記憶體晶片於3D堆疊中,會需要額外的重分佈層,並伴隨相互連結長度的增加與效能的降級。在這種情況下會傾向避免增加TSVs到CPU晶片,而是以雙面封裝構型,透過基底將CPU整合到3D記憶體堆疊上。 該基底是有TSVs與高密度相互連結的矽。針對這種整合系統的測試載具,已經建立且電信參數已經評估過[5,6]。

對於成本驅使的應用,如智慧手機,如上述大的矽基底材可能因成本考量而 禁止使用,且傳統的PoP封裝可能需要升級。一種做法是微縮在頂部與底部封裝之間的垂直相互連結的節距,並且將這些相互連結數量與記憶體匯流排的頻寬放大四倍[7,8]。雖然此機械式方法可以增加頻寬,但不像基於TSV的解決方案,他沒辦法降低I/O功率的損耗,因為並沒有做任何如前面討論(圖三)的減少相互連結寄生電容的動作。

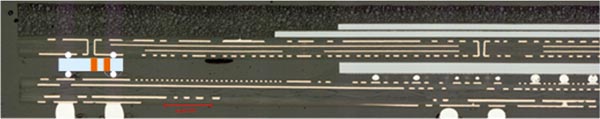

一種新穎的概念「主動式相互連結」已在APSTL被提出及發展中。此概念使用一種比較電子的方式來追上TSVs的效能[1]並取代這些機械式複雜的侵入實體矽晶片。額外IC上的補償電路被插入智慧手機的傳統PoP封裝的相互連結路徑上(圖四),如此形成超級PoP封裝有著接近基於TSV的3D堆疊之頻寬及功率效率,卻不需插入任何麻煩的TSVs到主動的晶片本身。

圖4.研發中能追上基於TSV的3D堆疊效能的APSTL超級PoP封裝之切面。在智慧手機的PoP兩層之間插入針對每個相互連結有著補償電路的積體電路。此晶片包含了穿通孔洞卻也避免在高價值的SoC或DRAM晶粒中插入TSVs。

結論

許多提供給晶片與系統設計者的封裝層級整合技術已於本文中討論。封裝層級相互連結的效能已經變的對系統效能在頻寬及功率效率方面而言愈加重要。傳統透過微縮相互連結長度及用最新迭代持續增加他們密度來改善封裝電子效能的方 式,就是TSVs。如同以往的創新,TSVs也遭遇機械式的複雜化,只是現在更加嚴重因為TSVs的應力影響到元件的效能。

TSV技術的未來發展必須不僅解決目前主流技術的所有殘餘問題,包含銅填充孔洞及併行晶圓薄化,還要在任何有可能之處做製程簡化。這包含採用更成功的材料(銅覆蓋的鎢穿孔)與製程選擇(晶圓薄化和黏合順序)在既有的生產上。目前創新的概念如主動式相互連結可以完全避免使用TSVs,且APSTL的超級PoP使用此概念在成本驅動與功率敏感的應用如智慧手機上顯示了正向訊息。SST-AP/Taiwan

參考文獻

- Gupta, D., “A novel non-TSV approach to enhancing the bandwidth in 3D packages for processor- memory modules “, IEEE ECTC 2013, pp 124 – 128.

- Karim, M. et al , “Power Comparison of 2D, 3D and 2.5D Interconnect Solutions and Power Optimization of Interposer Interconnects,” IEEE ECTC 2013, pp 860 – 866.

- Dutoit, D. et al, “A 0.9 pJ/bit, 12.8 GByte/s WideIO Memory Interface in a 3D-IC NoC-based MPSoC,” 2013 Symposium on VLSI Circuits Digest of Technical Papers.

- Yang, J-S et al, “TSV Stress Aware Timing Analysis with Applications to 3D-IC Layout Optimization,” Design Automation Conference (DAC), 2010 47th ACM/IEEE , June 2010.

- Tzeng, P-J. et al, “Process Integration of 3D Si Interposer with Double-Sided Active Chip Attachments,” IEEE ECTC 2013, pp 86 – 93.

- Beyene, W. et al, “Signal and Power Integrity Analysis of a 256-GB/s Double-Sided IC Package with a Memory Controller and 3D Stacked DRAM,” IEEE ECTC 2013, pp 13 – 21.

- Mohammed, I. et al, “Package-on-Package with Very Fine Pitch Interconnects for High Bandwidth,” IEEE ECTC 2013, pp 923 – 928

- Hu, D.C., “A PoP Structure to Support I/O over 1000,” ECTC IEEE 2013, pp 412 – 416

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

更多歷期精采文章,請參閱智權報總覽 >>

|